Vhdl Binary To Integer Converter Online

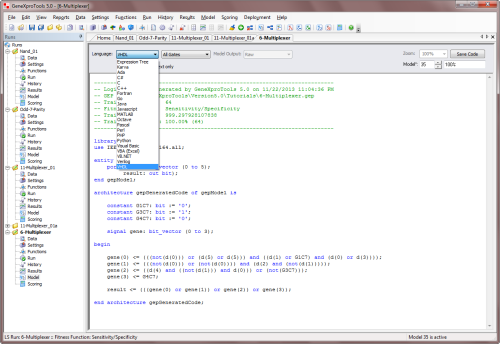

Hi, to convert std_logic_vector to integer use conv_integer(std_logic_vector_signal). To convert integer to std_logic_vector use conv_std_logic_vector(integer_signal, num_bits). Download Free Wild Game Innovations Camera Reviews. Num_bits are the number of bits the resulting std_logic_vector signal will have. For example: signal sig1: std_logic_vector(15 downto 0):=X'0123'; signal sig2: integer range 0 to 65535:=0; signal sig3: integer range 0 to 65535:=456; signal sig4: std_logic_vector(15 downto 0):=X'0000'; --To convert sig1-->Native Instruments B4ii Keygen Torrent. sig2 sig2sig4 sig4. Matthias.meurer wrote: Hi, to convert std_logic_vector to integer use conv_integer(std_logic_vector_signal). To convert integer to std_logic_vector use conv_std_logic_vector(integer_signal, num_bits). Num_bits are the number of bits the resulting std_logic_vector signal will have.

Is it possible to convert the input data in binary form (std_logic_vector) to integer in VHDL? The converted integer data is used to perform. Is it possible to convert the input data in binary form (std_logic_vector) to integer in VHDL? The converted integer data is used to perform.

Answer to Write a VHDL description of a BCD-to-Binary converter. Initially a three-digit BCD number is placed in the A register. I am stuck in the following problem- I need to write a VHDL function that converts 5 bit vector to integer where integer value of binary number a4a3a2a1a0 can be.

For example: signal sig1: std_logic_vector(15 downto 0):=X'0123'; signal sig2: integer range 0 to 65535:=0; signal sig3: integer range 0 to 65535:=456; signal sig4: std_logic_vector(15 downto 0):=X'0000'; --To convert sig1-->sig2 sig2sig4 sig4. Maharjanmilan wrote: Hi! Is it possible to convert the input data in binary form (std_logic_vector) to integer in VHDL? The converted integer data is used to perform some fixed point calculations using AccelDSP from xilinx. Once the calculations are made,the output generated from the AccelDSP is integer and my second question is, is it possible to convert back the result into std_logic_vector again?

Milan Look up the functions in the numeric_std library. See Ashenden's book for some good help. Your conversion functions depend on whether the binary value represents a signed or an unsigned number. The numeric_std library adds proper signed and unsigned types. So, for example, at the top of your source, add: use numeric_std.all. At the declarative part of the architecture (between the architecture keyword and the begin): signal foo_slv: std_logic_vector(15 downto 0); -- a 16-bit binary vector signal foo_us: unsigned(15 downto 0); -- a 16-bit unsigned vector signal foo_int: natural range 0 to 65535; -- a 16-bit natural (non-negative integer) and in the main body of the architecture: -- going from SLV to integer: foo_slv.